# A Practical SPICE Model Based on the Physics and Characteristics of Realistic Single-Electron Transistors

Sang-Hoon Lee, Dae Hwan Kim, Kyung Rok Kim, Jong Duk Lee, *Member, IEEE*, Byung-Gook Park, *Member, IEEE*, Young-Jin Gu, Gi-Young Yang, and Jeong-Taek Kong, *Member, IEEE*

Abstract—A practical model for a single-electron transistor (SET) was developed based on the physical phenomena in realistic Si SETs, and implemented into a conventional circuit simulator. In the proposed model, the SET current calculated by the analytic model is combined with the parasitic MOSFET characteristics, which have been observed in many recently reported SETs formed on Si nanostructures. The SPICE simulation results were compared with the measured characteristics of the Si SETs. In terms of the bias, temperature, and size dependence of the realistic SET characteristics, an extensive comparison leads to good agreement within a reasonable level of accuracy. This result is noticeable in that a single set of model parameters was used, while considering divergent physical phenomena such as the parasitic MOSFET, the Coulomb oscillation phase shift, and the tunneling resistance modulated by the gate bias. When compared to the measured data, the accuracy of the voltage transfer characteristics of a single-electron inverter obtained from the SPICE simulation was within 15%. This new SPICE model can be applied to estimating the realistic performance of a CMOS/SET hybrid circuit or various SET logic architectures.

*Index Terms*—MOSFET, realistic single-electron transistor, single-electron inverter, SPICE model.

#### I. INTRODUCTION

**M** OTIVATED by the merits of density, power, and functionality, various structures of single-electron transistors (SETs) have been recently demonstrated. From the viewpoint of the new functionality of SETs such as the CMOS/SET hybrid circuit system, the development of a simulation scheme using a conventional circuit simulator is an emerging challenge. While the previously reported simulation techniques were based on a numerical calculation of a master equation or a Monte Carlo method [1]–[4], these methods are often time-consuming, and cannot be easily expanded to a CMOS/SET hybrid circuit. Macro-model [5] and analytical SET models [6] for conventional SPICE simulators have recently been proposed and suc-

Manuscript received June 7, 2002; revised October 23, 2002. This work was supported by the BK 21 Program, by the Ministry of Commerce, Industry, and Energy under the "Functional Nano-Device and Circuit Application Technology Development Project," and by the national program for the "Tera-bit Level Nano Device Project" as a part of the 21st Century Frontier Project.

S.-H. Lee, D. H. Kim, K. R. Kim, J. D. Lee, and B.-G. Park are with the Inter-University Semiconductor Research Center, School of Electrical Engineering, Seoul National University, Seoul 151-742, Korea (e-mail: shoon.lee@samsung.com; bgpark@snu.ac.kr).

Y.-J. Gu, G.-Y. Yang, and J.-T. Kong are with Computer-Aided Engineering, Semiconductor Research and Development Division, Samsung Electronics Corporation Ltd., Kyungki-Do, Korea.

Digital Object Identifier 10.1109/TNANO.2002.807394

cessfully verified in terms of their usefulness and accuracy. Nevertheless, these models are unsatisfactory for analyzing and optimizing the performance of SETs in a real chip, because they are validated by a comparison with the Monte Carlo simulation results rather than actual experimental data.

In this study, a practical SPICE model based on the physical phenomena in realistic Si SETs was developed, and implemented into a conventional SPICE circuit simulator. The SPICE simulation results were compared with the measured characteristics of Si SETs. The distinctiveness of our model is that a single set of model parameters is used, while still considering divergent physical phenomena such as the parasitic MOSFET, the Coulomb oscillation phase shift, and tunneling resistance modulated by the gate bias. Secondly, estimation of the model parameters is intuitively possible, because this model begins from the analytic model, and includes the physical meaning of its parameters. The paper is ordered as follows. In Section II, the geometrical structure and electrical characteristics of the fabricated SETs, which are reported elsewhere [7], [8], are briefly reviewed. In Section III, the details in implementing the physical phenomena and structure of the realistic SETs are presented. Finally, the SPICE simulation results of our model are compared with the experimental characteristics of the Si SETs and the reliability of our model is confirmed in Section IV.

#### II. DEVICE STRUCTURE AND ELECTRICAL CHARACTERISTICS

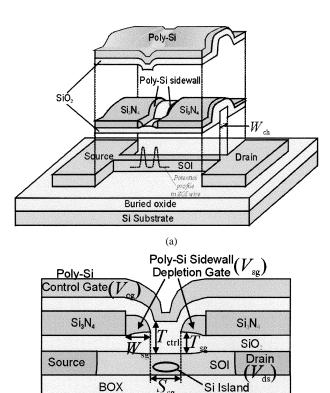

Fig. 1 shows a schematic diagram of the device structure and cross section of the SET with sidewall depletion gates on an silicon-on-insulator (SOI) nanowire [7]. An electrically induced Coulomb island is formed in the 30-nm-wide channel ( $W_{\rm ch}$ ) of the SOI MOSFET by the field effect of the sidewall depletion gate bias. This device shows good controllability and reproducibility over a wide range of temperatures (4.2 K~77 K). Detailed information about its fabrication is reported elsewhere [8]. In particular, the island size ( $S_{\rm sg}$ ) is split in the range of 40~190 nm with the aim of controlling the electrical behavior of the SETs. This allows the size of the island to be considered as a design parameter, which can further optimize the performance of SET logic circuit. For example, the logical "HIGH" voltage is given by half the period of the Coulomb oscillation in most SET logic circuitry.

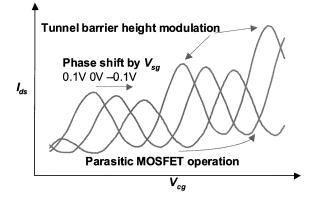

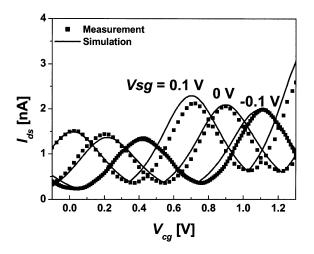

Fig. 2 shows the electrical characteristic of the fabricated SETs. While the Coulomb oscillation is shown with a sweeping control gate voltage  $(V_{cg})$ , three physical phenomena that are

Si Substrate Back Gate (b)

$(V_{bg})$

Fig. 1. (a) Schematic diagram of the fabricated Si SETs with sidewall depletion gates and (b) cross-sectional view of (a). Here, the island size  $S_{\rm sg}$  can be controlled over the range 40–190 nm.

Fig. 2. Typical electrical characteristics of the fabricated SETs. The device with an island size  $S_{sg} = 40$  nm was measured at 77 K ( $V_{ds} = 5$  mV and  $V_{sg}$  ranges from -0.1 to 0.1 V).

distinguished from the *orthodox theory* are clearly observed in the realistic SETs. First of all, the phase of the Coulomb oscillation is shifted by the sidewall depletion gate voltage ( $V_{\rm sg}$ ), which is useful from the point of view of SET logic. Secondly, the peak-to-valley current ratio (PVCR) decreases as the  $V_{\rm cg}$  increases, due to the parasitic MOSFET effect [9]; i.e., the poly-Si control gate accumulates electrons in the Si layer under the gate, and controls the electrostatic potential of the SET island (the area of  $W_{\rm ch} \times S_{\rm sg}$ ). This is reasonable in that a MOSFET is inevitably formed in a Si nanowire, which is also the case in various SETs with a physically formed Si island [9], [10]. Thirdly, the level of the SET current increases as the control gate voltage

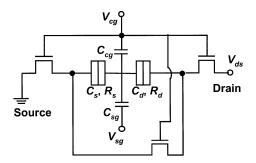

Fig. 3. Equivalent circuit model for the fabricated Si SETs with sidewall depletion gates.

Fig. 4. Transfer characteristics of the fabricated SETs as a function of temperature. The device with an island size  $S_{\rm sg}=40$  nm is measured at  $V_{\rm ds}=5$  mV and  $V_{\rm sg}=-0.1$  V.

$(V_{cg})$  increases, as a result of the tunnel barrier height modulation by the  $V_{cg}$ .

Fig. 3 shows the equivalent circuit diagram of the fabricated device, which is composed of an SET and three parasitic MOSFET's from Fig. 1, i.e., one MOSFET is parallel connected to the SET and the other two are series connected to the SET. While the two serial parasitic MOSFETs have the long channel length ( $L = 3.5 \ \mu m$ ) and narrow width ( $W_{ch} = 30 \ nm$ ) from source (or drain) to island in Fig. 1, the parallel MOSFET have short channel length [L = island size + 2 × (sidewall depletion gate width)] and narrow width ( $W_{ch} = 30$  nm). The parallel MOSFET is not an entity physically separate from the SET, but represents the MOSFET-like current component in the SET structure due to higher energy electrons at higher temperature. In case of the SET, it has two tunnel junctions and additional capacitors.  $R_d$  and  $R_s$  are the tunneling resistances of the respective tunnel junctions. The charge of an electrically formed Si island is capacitively coupled with four capacitors, which are the control gate capacitance  $(C_{cg})$ , the source tunnel junction capacitance  $(C_s)$ , the drain tunnel junction capacitance  $(C_d)$ , and the sidewall depletion gate capacitance  $(C_{sg})$ . The back gate capacitance is assumed to be negligible due to a relatively thicker buried oxide rather than the control gate oxide.

#### III. IMPLEMENTATION OF THE CURRENT-VOLTAGE MODEL

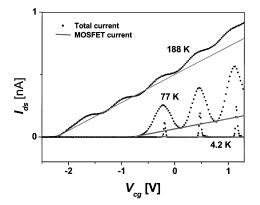

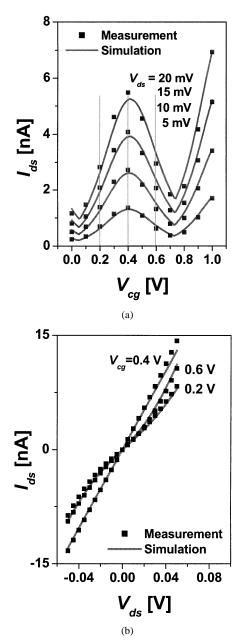

In addition to the SET current ( $I_{SET}$ ), parasitic MOSFET currents inherently exist in our device. Fig. 4 shows typical experimental I-V characteristics at various temperatures. When

the control gate voltage is lower than the threshold voltage of two series-connected parasitic MOSFETs, they act as a high resistance, causing the Coulomb oscillation to vanish. As the control gate voltage increases above the threshold voltage, however, their resistance becomes low, so that we can ignore their existence. Hence, the total current (symbols) can be approximately decomposed into two components: the Coulomb oscillation of the SET and parallel-connected MOSFET current (solid lines).

The SPICE model for the realistic SETs was implemented in two parts. The total drain current is given by

$$I_{\rm ds} \cong I_{\rm SET} + I_{\rm MOSFET} \tag{1}$$

where  $I_{\text{SET}}$  and  $I_{\text{MOSFET}}$  are the SET current based on a simple capacitive Coulomb blockade model (i.e., *orthodox theory*) and a parasitic MOSFET current, respectively.

# A. SET Current $(I_{SET})$

The basic formulation for the SET current is based on the analytical model proposed by Uchida *et al.* [6]. The analytical equation for the I-V characteristics of the SET having N or N+1 electrons in its island is given by

$$I_{\rm SET} = \frac{e}{2R_{\Sigma}C_{\Sigma}} \frac{\left(\tilde{V}_{\rm cg}^2 - \tilde{V}_{\rm ds}^2\right)\sinh\left(\tilde{V}_{\rm ds}/\tilde{T}\right)}{\left[\tilde{V}_{\rm cg}\sinh\left(\tilde{V}_{\rm cg}/\tilde{T}\right) - \tilde{V}_{\rm ds}\sinh\left(\tilde{V}_{\rm ds}/\tilde{T}\right)\right]}$$

(2)

where  $\tilde{V}_{\rm ds} = C_{\Sigma} V_{\rm ds}/e$ ,  $\tilde{T} = 2k_B T C_{\Sigma}/e^2$ ,  $R_{\Sigma} = R_s + R_d$ ,  $C_{\Sigma} = C_{\rm cg} + C_s + C_d + C_{\rm sg}$ , and

$$\tilde{V}_{\rm cg} = \frac{2C_{\rm cg}V_{\rm cg}}{e} - \frac{(C_{\rm sg} + C_{\rm cg} + C_s - C_d)V_{\rm ds}}{e} - 1 - 2N.$$

(3)

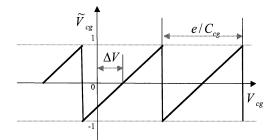

Despite its simplicity, this analytical model perfectly reproduces the numerically calculated characteristics even in the case of a relatively high drain voltage and temperature [6]. While this result is encouraging, two important issues still remain. These are the physical effects in the real SETs, and being able to achieve a simpler form so as to incorporate the analytical equation into a conventional circuit simulator. To resolve this problem, the periodic function  $\tilde{V}_{cg}$  in (1) was expressed in a simplified form as follows:

$$\tilde{V}_{\rm cg} = 2 \left[ \frac{C_{\rm cg}}{e} (V_{\rm cg} - \Delta V) - \operatorname{int} \left( \frac{C_{\rm cg}}{e} (V_{\rm cg} - \Delta V) + 0.5 \right) \right]$$

(4)

where "int(x)" returns the largest integer  $\leq x$  and the phase shift  $\Delta V$  is given by

$$\Delta V = \frac{e}{2C_{\rm cg}} + \frac{(C_{\rm sg} + C_{\rm cg} + C_s - C_d)V_{\rm ds}}{2C_{\rm cg}}.$$

(5)

As shown in Fig. 5, (4) takes on the periodic function of  $V_{cg}$  with the period of  $e/C_{cg}$  and the phase shift of  $\Delta V$ , and it is identical to one in (3). Eventually, implementing (2) and (4) into the conventional SPICE simulator is straightforward, as the circuit elements are composed of voltage-controlled current sources and voltage-controlled voltage sources.

The phase shift in Coulomb oscillation by the  $V_{\rm sg}$  can be implemented by modifying  $\Delta V$ . The relationship between  $V_{\rm sg}$  and

Fig. 5. Normalized  $\bar{V}_{\rm gs}$  of (4) is plotted as a function of  $V_{\rm cg}$  ranging from -1 to 1.

$V_{\rm cg}$  can be derived by the following equation based on the conservation of island charge:

$$\Delta V_{\rm cg} = -\frac{2C_{\rm sg}}{C_{\rm cg}} \,\Delta V_{\rm sg}.\tag{6}$$

Adding the right term of (6) to (5), the final phase shift  $\Delta V$  of the Coulomb oscillation is given by

$$\Delta V = \frac{e}{2C_{\rm cg}} + \frac{(C_{\rm sg} + C_{\rm cg} + C_s - C_d)V_{\rm ds}}{2C_{\rm cg}} - \frac{2C_{\rm sg}}{C_{\rm cg}}V_{\rm sg}.$$

(7)

In addition, the SET current increases as the  $V_{cg}$  increases, since the electrically induced tunnel barrier by the  $V_{sg}$  is lowered [8], as shown in Fig. 2. Such *tunnel barrier lowering* effect is simply included by substituting the total resistances of the tunnel junctions of (2) with (8)

$$R_{\Sigma} = R_{\Sigma} \exp[(\text{TBL}(V_{\text{cg}} - V_{\text{th}})] \tag{8}$$

where  $V_{\rm th}$  is the threshold voltage of the parasitic MOSFETs, which are described in the next section, and TBL is a fitting parameter.

### B. Parasitic MOSFET Current $(I_{MOSFET})$

The basic formulation of the parasitic MOSFET is based on the SPICE LEVEL 3 MOSFET model, where the drain current model includes the temperature dependence of both the threshold voltage and the mobility. The model was modified as shown in (9)-(11)

$$I_{\text{MOSFET}} = \text{CAL} \frac{\mu(T) \cdot W_{\text{ch}} \cdot C_{\text{OX}}}{S_{\text{sg}} + 2W_{\text{sg}}} \cdot [(V_{\text{cg}} - V_{\text{th}})V_{\text{ds}}] \cdot f(T)$$

(9)

$$\mu(T) = U0 \cdot (T/300)^{\text{BEX}}$$

(10)

$$V_{\rm th} = \mathsf{VT0} + \mathsf{DT} \cdot k_b T/q \tag{11}$$

where  $C_{OX}$  is the control gate oxide capacitance,  $W_{sg}$  is the width of the sidewall depletion gate, VT0 is the zero temperature threshold voltage, U0 is the mobility at 300 K, and both BEX and CAL are fitting parameters. The second term in (11) is used to account for the temperature dependence of the threshold voltage, as shown in Fig. 4, including the fitting parameter DT.

Besides the threshold voltage change versus temperature, it was observed that, as the temperature increases from 4.2 K to 188 K, the slope of the current increases, which contrasts with the temperature dependence of the mobility in a conventional

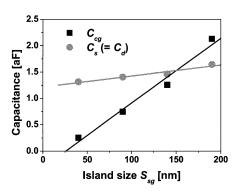

Fig. 6. Island size dependence of the device parameters. The linear regression lines agree well with the measured data obtained from 21 dies. Here, ALPHA and BETA are  $1.2 \times 10^{-17}$  and  $2.1 \times 10^{-18}$ , respectively.

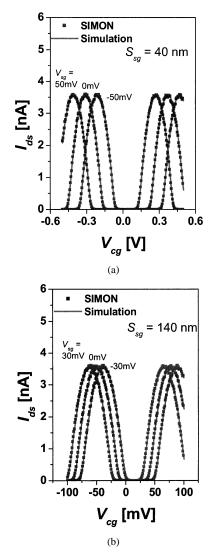

Fig. 7. SET I-V characteristics using the SET SPICE model and the simulator, SIMON, for various  $V_{\rm sg}$  at 4.2 K.  $V_{\rm ds}=20$  mV and  $R_s=R_d=1.4~{\rm M}\Omega.$  (a)  $C_s=C_d=1.3~{\rm aF}, C_{\rm cg}=0.24~{\rm aF}$  (corresponding to  $S_{\rm sg}=40$  nm), and  $V_{\rm sg}$  ranges from -50 to 50 mV. (b)  $C_s=C_d=1.46$ ,  $C_{\rm cg}=1.26~{\rm aF}$  (corresponding to  $S_{\rm sg}=140$  nm), and  $V_{\rm sg}$  ranges from -30 to 30 mV.

Si MOSFET. In order to understand this unusual behavior, the thermally activated conduction through the two tunnel barriers electrically induced by the  $V_{\rm sg}$  should be considered. The

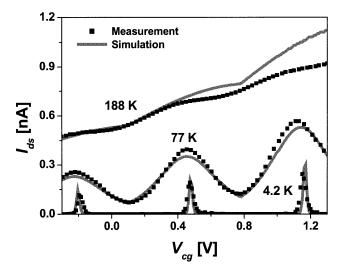

Fig. 8. SET I-V characteristics of the SETs at various temperatures ( $V_{\rm ds} = 1 \text{ mV}$ ,  $V_{\rm sg} = -1 \text{ V}$ ). Here,  $C_{\rm cg} = 0.24$  aF and  $C_s = C_d = 1.3$  aF (corresponding to  $S_{\rm sg} = 40$  nm).

Fig. 9. SET I-V characteristics of at various sidewall gate biases at 77 K ( $V_{\rm ds}=5$  mV). Here,  $C_{\rm cg}=0.24$  aF and  $C_s=C_d=1.3$  aF (corresponding to  $S_{\rm sg}=40$  nm).

electrical behavior of the parasitic MOSFET can be modeled as thermionic emission transport, as is the case in a Schottky barrier diode [11], where the current density is given by the concentration of electrons with energies sufficient to overcome the potential barrier by the sidewall depletion gates. Thus, the thermionic emission current term f(T) in (9) is given by

$$f(T) = \operatorname{RA} \cdot T^2 \exp\left(-\frac{q\Phi_B}{kT}\right)$$

(12)

where  $\Phi_B$  is the barrier height of the tunnel junctions and RA is the normalized Richardson constant.

# C. Island Size Dependence of I-V Characteristics

The SPICE model for the island size dependence of the device characteristics in the fabricated SETs was implemented in two parts. For the parasitic MOSFETs, the parameter,  $S_{sg}$ , for island size is considered in (9). On the other hand, in our previous work [9], it was found that both  $C_{cg}$  and  $C_d$  extracted from the SET characteristics can be represented as a linear function of

Fig. 10. I-V characteristics of the SET at various  $V_{\rm ds}$  at 77 K. Here,  $S_{\rm sg}=40$  nm,  $C_s=C_d=1.3$  aF,  $C_{\rm cg}=0.24$  aF. (a)  $V_{\rm cg}-I_{\rm ds}$  curves and (b)  $V_{\rm ds}-I_{\rm ds}$  curves.

the island size,  $S_{sg}$ , as illustrated in Fig. 6. The island size can be implemented into our model using the following equations:

$$C_{\rm cg} = {\rm ALPHA} \; \frac{S_{\rm sg} \cdot W_{\rm ch}}{T_{\rm ctrl}} \tag{13}$$

$$C_d(=C_s) = \text{BETA} \ \frac{W_{\text{ch}}}{W_{\text{sg}}} S_{\text{sg}}$$

(14)

where  $T_{\text{ctrl}}$  is the thickness of the control gate oxide, and both ALPHA and BETA are fitting parameters.

## IV. COMPARISON WITH EXPERIMENTAL RESULTS

In order to validate our model, the I-V characteristics at 4.2 K (at this temperature, a parasitic MOSFET is fully turned off) calculated by our SPICE model were first compared with

Fig. 11.  $I{-}V$  characteristics of the SET at various island sizes  $S_{\rm sg}$  at 77 K ( $V_{\rm ds}$  = 10 mV, 77 K).

TABLE I MODEL PARAMETERS FOR THE FABRICATED SETS AND THEIR TYPICAL VALUES USED IN THE CALCULATIONS

| Name                  | Unit                  | Meaning                              | Value                 |

|-----------------------|-----------------------|--------------------------------------|-----------------------|

| S <sub>sg</sub>       | nm                    | Island size                          | 40, 90, 140           |

| W <sub>sg</sub>       | nm                    | Width of the sidewall depletion gate | 30                    |

| W <sub>ch</sub>       | um                    | Width of SOI wire                    | 0.03                  |

| $R_s(R_d)$            | MΩ                    | Tunnel resistance                    | 1.40                  |

| $\overline{C_s(C_d)}$ | aF                    | Drain (Source) capacitance           | 1.30, 1.40, 1.46      |

| C <sub>cg</sub>       | aF                    | Control gate capacitance             | 0.24, 0.76, 1.26      |

| C <sub>sg</sub>       | aF                    | Sidewall gate capacitance            | 0.23                  |

| C <sub>ox</sub>       | F/cm <sup>2</sup>     | Gate oxide capacitance in MOSFET     | 1×10-9                |

| UO                    | Cm <sup>2</sup> /Vsec | Mobility at 300 K                    | 1500                  |

| RA                    | A/K <sup>2</sup>      | Normalized Richardson constant       | $1.44 	imes 10^{-11}$ |

| $\Phi_{\mathbf{B}}$   | eV                    | Tunnel barrier height                | 0.016                 |

| VT0                   | v                     | Threshold voltage at 0 K             | 0.23                  |

| BEX                   | NONE                  | Mobility parameter for temperature   | -1.95                 |

| DT                    | NONE                  | Fitting parameter                    | -100                  |

| CAL                   | NONE                  | Fitting parameter                    | 2.3 × 10-9            |

those obtained from the Monte Carlo simulation, as shown in Fig. 7. The symbols represent the results calculated by the single-electron circuit simulator SIMON [2]. The simulation results from the SPICE model reproduce the Coulomb oscillation phase shift accurately in the case of two SETs with the different island sizes. This means that by using the simplification used in our model, the analytical SET model can be reasonably incorporated into the SPICE model.

The simulation result from our SPICE model was then compared with the experimental data from the fabricated SETs. First, the temperature dependence of the Coulomb oscillation from our SPICE model was compared with the measured I-Vcharacteristics of the SETs, as shown in Fig. 8. Here, it should be emphasized that the two valley currents agree very well with each other, because the parasitic MOSFET effect is accurately reproduced in our SPICE model. Furthermore, the line shape of the Coulomb oscillation peak and its temperature dependence also agree with each other. This suggests that the assumption of both the tunnel barrier lowering and the thermionic emission current is quite reasonable and was successfully implemented

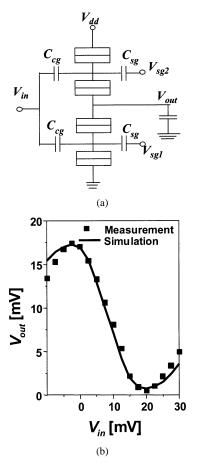

Fig. 12. (a) Circuit diagram for a complementary SET inverter consisting of two SETs in series and (b) simulated voltage transfer characteristics. Here,  $V_{dd} = 20$  mV,  $C_s = C_d = 1.6$  aF, and  $C_{cg} = 2.1$  aF, and the load capacitance  $C_L = 500$  pF.

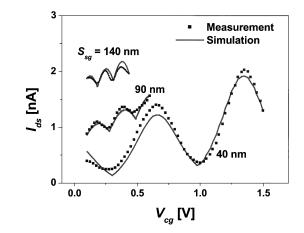

into our SPICE model. Secondly, the  $V_{\rm sg}$  dependence of the Coulomb oscillation from our SPICE model was compared with the measured I-V characteristics of the SETs, as shown in Fig. 9. The Coulomb oscillation phase shift by  $V_{\rm sg}$  was well reproduced, and in good agreement with the measured data. Thirdly, the  $V_{\rm ds}$  dependence of the I-V characteristics from our SPICE model was compared with the measured I-V characteristics of the SETs, as shown in Fig. 10.

Furthermore, the I-V characteristic dependence on the island size was simulated, as shown in Fig. 11. The model parameter values used are shown in Table I. In particular, only one set of parameters is needed to simulate the I-V characteristics. Our model provides a good accuracy for an island size of  $S_{sg} = 40$ nm, 90 nm, and 140 nm at 77 K.

Finally, based on our model, a SPICE simulation was performed for a complementary SET inverter, as shown in Fig. 12. The accuracy of the voltage transfer characteristics of an SET inverter obtained from the SPICE simulation was within 15% of the measured data.

### V. CONCLUSION

A practical SPICE model for real Si SETs was developed based on a simple analytical model and its appropriate modification. This new SPICE model can reproduce not only the typ-

#### REFERENCES

- M. Kirihara, N. Kuwamura, K. Taniguchi, and C. Hamaguchi, "Monte Carlo study of single-electron devices," in *Abstracts Int. Conf. Solid State Devices and Materials*, Yokohama, Japan, 1994, pp. 328–330.

- [2] C. Wasshuber, H. Ksoina, and S. Selberherr, "SIMON—A simulator for single-electron tunnel devices and circuits," *IEEE Trans. Computer-Aided Design*, vol. 16, pp. 937–944, Sept. 1997.

- [3] M. Fujishima, S. Amakawa, and K. Hoh, "Circuit simulators aiming at single-electron integration," *Jpn. J. Appl. Phys.*, vol. 37, pp. 1478–1482, 1998.

- [4] M. Kirihara, K. Nakazato, and M. Wagner, "Hybrid circuit simulator including a model for single electron tunneling devices," *Jpn. J. Appl. Phys.*, vol. 38, pp. 2028–2032, 1999.

- [5] Y. S. Yun, S. W. Hwang, and D. Ahn, "Macromodeling of single-electron transistors for efficient circuit simulation," *IEEE Trans. Electron Devices*, vol. 46, pp. 1667–1671, Aug. 1999.

- [6] K. Uchida, K. Matsuzawa, J. Koga, R. Ohba, S. Takagi, and A. Toriumi, "Analytical single-electron transistor (SET) model for design and analysis of realistic SET circuits," *Jpn. J. Appl. Phys.*, vol. 39, pp. 2321–2324, 2000.

- [7] D. H. Kim, S. K. Sung, K. R. Kim, B. H. Choi, S. W. Hwang, D. Ahn, J. D. Lee, and B. G. Park, "Si single-electron transistors with sidewall depletion gates and their application to dynamic single-electron transistor logic," in *IEDM Tech. Dig.*, 2001, pp. 151–154.

- [8] D. H. Kim, S.-K. Sung, K. R. Kim, J. D. Lee, B.-G. Park, B. H. Choi, S. W. Hwang, and D. Ahn, "Silicon single-electron transistors with side-wall depletion gates and their application to dynamic single-electron transistor logic," *IEEE Trans. Electron Devices*, vol. 49, pp. 627–635, Apr. 2002.

- [9] A. Fujiwara, Y. Takahashi, H. Namatsu, K. Kurihara, and K. Murase, "Suppression of effects of parasitic metal–oxide–semiconductor fieldeffect transistors on Si single-electron transistors," *Jpn. J. Appl. Phys.*, vol. 37, pp. 3257–3263, 1998.

- [10] H. Ishikuro and T. Hiramoto, "Fabrication of nano-scale point contact metal-oxide-semiconductor field-effect-transistors using micrometerscale design rule," *Jpn. J. Appl. Phys.*, vol. 38, pp. 396–398, 1999.

- [11] H. Fukui, M. Fujishima, and K. Hoh, "Single-electron transistor in silicon-on-insulator with Schottky-contact tunnel barriers," *Jpn. J. Appl. Phys.*, vol. 36, pp. 4147–4150, 1997.

Sang-Hoon Lee received the B.S. degree in computer science and statistics from Seoul National University, Seoul, Korea, in 1990. Since 2001, he has been working toward the M.S. degree in the School of Electrical Engineering, Seoul National University.

In 1990, he joined the Computer-Aided Engineering team of Samsung Electronics, Kyungki-Do, Korea, where he was involved in the research of TCAD and statistical SPICE modeling. His current research interest is SPICE modeling for single-electron transistors.

**Dae Hwan Kim** was born in Korea on October 24, 1972. He received the B.S., M.S., and Ph.D. degrees from the School of Electrical Engineering, Seoul National University, Seoul, Korea, in 1996, 1998, and 2002, respectively.

Since 1992, he has been engaged in circuit design of DRAM at Samsung Electronics Corporation, Kyungki-Do, Korea. His current research interests are Si nanoelectronic devices and nanoscale CMOS devices.

**Kyung Rok Kim** received the B. S. and M.S. degrees in 1999 and 2001, respectively, from the School of Electrical Engineering, Seoul National University, Seoul, Korea, where he is currently working toward the Ph.D. degree.

His current research interest is the Si quantum tunneling device.

Young-Jin Gu received the B.S. degree in electrical engineering from Kyungpook National University, Daegu, Korea, in 1991.

In 1991, he joined Computer-Aided Engineering, Semiconductor Research and Development Division, Samsung Electronics Corporation Ltd., Kyungki-Do, Korea, where he is currently working as a Senior Engineer in the area of circuit/RF simulation.

**Jong Duk Lee** (M'79) was born in Youngchun, Korea, in 1944. He received the B.S. degree in physics from Seoul National University, Seoul, Korea, in 1966, and the Ph.D. degree from the Department of Physics, University of North Carolina, Chapel Hill, in 1975.

He was an Assistant Professor in the Department of Electronics Engineering, Kyungpook National University, from 1975 to 1978. In 1978, he studied microelectric technology at HP-ICL, Palo Alto, CA, and soon afterward worked for the Korea Institute of

Electronic Technology (KIET) as the Director of the semiconductor division. He established the KIET Kumi Facility and introduced the first polysilicon gate technology in Korea by developing 4K SRAM, 32K, and 64K Mask ROMs, and one-chip 8-bit microcomputers. In July 1983, he moved to the Department of Electronics Engineering, Seoul National University, as an Associate Professor, which merged with the School of Electrical Engineering in 1992, where he has been a Professor since 1988. He established the Inter-University Semiconductor Research Center (ISRC) in 1985, and served as the Director until 1989. He served as the Chairman of the Electronics Engineering Department from 1994 to 1996. He was with Samsung Display Devices Company, Ltd., as the Head of Display R&D Center in 1996, on leave from Seoul National University. He concentrated his study on image sensors such as Vidicon type, MOS type, and also CCDs, for Samsung Display Devices Company and Samsung Electronics Company from 1984 to 1991. His current research interests include sub-0.1  $\mu$ m CMOS structure and technology, FEDs, CMOS image sensors, and high-speed SRAM design. He has published over 130 papers in major international scientific journals, including over 65 SCI papers. He has presented more than 180 papers, including 80 international conference papers. He also has registered 11 U.S., three Japanese, and eight Korean patents.

Dr. Lee is the member of the Steering Committees for the International Vacuum Microelectronics Conference (IVMC) and Korean Conference on Semiconductors (KCS). He was the Conference Chairman of IVMC'97 and KCS'98 who led the IVMC'97 and the KCS'98. He was also a member of the International Electron Devices Meeting (IEDM) Subcommittee on Detectors, Sensors, and Displays operated by the IEEE Electron Devices Society from 1998 to 1999. In June 1999, he was elected First President of the Korean Information Display Society.

**Byung-Gook Park** (M'96) received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1982 and 1984, respectively, and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 1990.

From 1990 to 1993, he was with AT&T Bell Laboratories, Murray Hill, NJ, where he contributed to the development of 0.1- $\mu$ m CMOS and its characterization. From 1993 to 1994, he was with Texas Instruments Incorporated, Dallas, TX, developing 0.25- $\mu$ m

CMOS. In 1994, he joined the School of Electrical Engineering, Seoul National University, as an Assistant Professor. He is currently an Associate Professor. His current research interests are nanoscale CMOS devices, Si single-electron devices, organic electroluminescent displays, and scanning probe microscopy systems.

Dr. Park was a member of the International Electron Devices Meeting (IEDM) Subcommittee on Solid State Devices, operated by the IEEE Electron Devices Society, from 2001 to 2002.

**Gi-Young Yang** received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute Science and Technology, Taejon, Korea, in 1992, 1994, and 1999, respectively.

In 1999, he joined Computer-Aided Engineering, Semiconductor Research and Development Division, Samsung Electronics Corporation Ltd., Kyungki-Do, Korea, where he is currently working as a Senior Engineer in the area of circuit modeling of MOSFETs.

Jeong-Taek Kong (S'91–M'95) received the B.S. degree in electronics engineering from Hanyang University, Hanyang, Korea, in 1981, the M.S. degree in electronics engineering from Yonsei University, Yonsei, Korea, in 1983, and the Ph.D. degree in electrical engineering from Duke University, Durham, NC, in 1994.

From 1983 to 1990, he was with Samsung Electronics Company, Ltd., as a VLSI CAD Manager. From 1990 to 1994, he was at Duke University granted by a Fellowship from Samsung Electronics

Company, Ltd. Currently, he is with the Semiconductor Research and Development Division, Samsung Electronics Corporation Ltd., Kyungki-Do, Korea, as Vice-President of the Computer-Aided Engineering team. He has authored or coauthored more than 60 technical papers published in international journals and conference proceedings and coauthored *Digital Timing Macromodeling for VLSI Design Verification* (Norwell, MA: Kluwer, 1995). His research interests focus on various VLSI CAD tools and design methodologies.

Dr. Kong has served on the program committees of IEEE International Workshop on Statistical Metrology, International Conference on VLSI and CAD, International Symposium on Quality of Electronic Design, and International Conference on Simulation of Semiconductor Processes and Devices. He is a Member of the Nanoelectronics and Giga-Scale Systems (NaGS) Technical Committee and serves as a Distinguished Lecturer for the IEEE Circuits and Systems Society. He is an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—PART II: ANALOG AND DIGITAL SIGNAL PROCESSING and IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATED (VLSI) SYSTEMS.